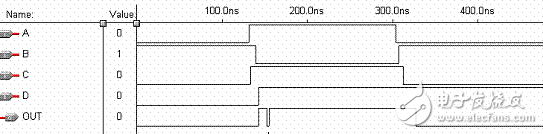

Adventure often affects the stability of logic circuits. The clock port, clearing and setting ports are very sensitive to glitch signals. Any glitch may cause the system to make an error. Therefore, judging whether there is risk in the logic circuit and how to avoid the risk are issues that designers must consider.

How to deal with glitches

Reduce the occurrence of burrs by changing the design and destroying the conditions of burrs. For example, in the design of digital circuits, Gray code counters are often used to replace ordinary binary counters. This is because the output of Gray code counters has only one transition at a time, which eliminates the occurrence of competitive risks and avoids the occurrence of glitches.

The glitch is not harmful to all inputs. For example, the D input of the D flip-flop, as long as the glitch does not appear on the rising edge of the clock and meet the data setup and hold time, it will not cause harm to the system. The D input of the trigger is not sensitive to glitches. According to this feature, we should use a synchronous circuit in the system as much as possible, because the signal changes of the synchronous circuit occur at the clock edge, as long as the glitch does not appear at the edge of the clock and does not meet the data establishment and retention time Will cause harm to the system. (Because the glitch is very short, mostly a few nanoseconds, it is basically impossible to meet the data establishment and retention time)

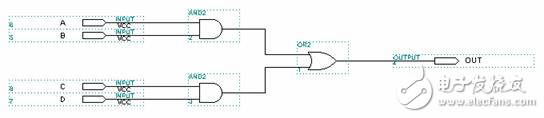

A common method of removing glitches is to use the D input of the D flip-flop to be insensitive to glitch signals. During the hold time of the output signal, the trigger is used to read the output signal of the combinational logic. This method is similar to the The asynchronous circuit is transformed into a synchronous circuit.

Portable energy storage power Stastion

SHENZHEN CHONDEKUAI TECHNOLOGY CO.LTD , https://www.szfourinone.com