The growth trend of design dimensions is unstoppable, which has always been a heavy burden for EDA verification tools. The dynamic power estimation tool is one of them.

There are always some stimuli that entice customers to upgrade their mobile devices frequently. These include more features and an improved user experience, a more attractive user interface, lighter weight, longer battery life, and much more. In all respects, it seems that lasting battery life ranks first, and longer battery life is directly related to lower power consumption.

Since Noyce and Kilby invented planar integrated circuits 50 years ago, the power consumption of microelectronics has experienced a period of steady decline. Planar technology makes it possible to scale (shrink) solid state devices. The smaller the transistor size, the more transistors there are in the same area, the faster the switching speed, the less energy is consumed, and the lower the temperature at which the chip operates (compared to the same number of transistors) Word).

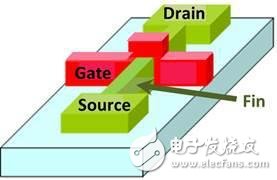

"Doublegate FinFET", Author: Irene Ringworm, published on the English Wikipedia. Authorized under the CC BY-SA 3.0 agreement via Wikimedia Commons.

Historically, the measurement of microelectronics development has focused on the length of the silicon channel between the source and drain of a field effect transistor (known as the process technology node). In the early 1960s, the node was 50 microns. Ten years later, this number dropped below 1 micron, and by 2003, it reached below 100 nanometers, opening the era of nanotechnology.

In the first two decades, due to leakage problems, the static power consumption when the transistors are not switched and idle is much smaller than the dynamic power consumption in the transistor switching state, which is negligible. At 180 nm, the static power consumption began to rise rapidly. By 2005, the static power consumption exceeded the dynamic power consumption due to the node dropping below 65 nm.

no need to worry. The invention of the FinFET or 3D transistor promptly pulled the planar transistor that slipped toward the disappearing abyss.

FinFETs are expected to reduce static leakage current by up to 90% and use only 50% of the dynamic power of an equivalent planar transistor. Compared to planar equivalent transistors, FinFET transistors run faster at the same power consumption or with lower power consumption at the same performance. With FinFET, the design team can better balance production, performance and power to meet the needs of individual applications.

Power estimation challenge

As mentioned earlier, lower process nodes result in higher transistor densities, giving design teams the opportunity to add more and more features to them. Today, in the largest designs, the number of transistors exceeds 10 billion. Unfortunately, the growth in design size is unstoppable, and this has always been a heavy burden for EDA verification tools. The dynamic power estimation tool is one of them. We can assume that the dynamic power consumption of the circuit is proportional to the number of logical transitions that occur when the circuit is running. Therefore, to accurately estimate and optimize the power of a digital circuit, we need to record the switching activity of each design element in each clock cycle and feed the activity into the tool to perform power-related tasks.

The average power consumption during the running period can be obtained by recording the switching activity without tracking the corresponding period. Peak power consumption can be tracked by adding information recorded in cycles.

We intuitively assume that the accuracy of the record switching activity will increase as the design specification drops from a high level abstraction to a gate level, and then to the transistor level, as more and more design details are available.

The dilemma is that at the electronic system level (ESL), designers have unprecedented flexibility in comparing multiple architectures, multiple scenarios or software algorithms and achieving optimal power optimization. Worse, at the instruction level, the power estimate is not accurate enough. At the gate level, there is minimal detail and flexibility, and only edge optimization is supported, especially at the transistor level. At the register transfer level (RTL), it seems that the best compromise can be achieved. Sufficient detailed information can be obtained to achieve an appropriate estimate of power and sufficient flexibility to achieve greater power optimization.

Dynamic power consumption is highly dependent on the activity within the design that is triggered by the excitation applied to its primary input device or embedded software executed by the embedded processor in the embedded SoC design era. That is, by starting the operating system or executing a driver, application, or diagnostic.

Verification engines such as simulators and emulators are the perfect tool for tracking switching activity. The caveat is that the simulator's execution speed depends primarily on the design level specification, design size, and the type of stimulus applied to the design. To mitigate and eliminate such dependencies, and to handle embedded software, only the simulator can perform this challenging task in a reasonable amount of time.

As of now, estimating power consumption has always been a two-step approach: In the first step, the simulator or simulator will track and accumulate switching activity throughout the run in a Swap Format (SAIF) file, or in the Fast Signal Database (FSDB). The switching activity of each signal is recorded in cycles in the file. In the second step, a power estimation tool fed into the SAIF file is used to calculate the average power consumption of the entire circuit, or a power estimation tool fed into the FSDB file is used to calculate the peak power in the design time and space.

The above mechanism has two problems for SoC design. SAIF and FSDB files are large and almost unmanageable and require long-term maintenance. In the era of one billion design, these two problems combined have made the above methods useless.

XPON,which can be used as both EPON and GPON.XPON 4GE ONU,it's including 1 PON PORT,4*GE network port,can be used as EPON 4GE ONU and GPON 4GE ONT.

XPON product fully complies with the ITU.984 standard,Carrier-grade equipment that is easy to operate, manage and maintain;It is a bridge home terminal device that realizes uwb access for home /SOHO users through XPON technology. structure, supporting the placement of desktop, wall hanging or placed in the corridor information box.

>Support IEEE802.3ah(EPON) and ITU-TG.984.x(GPON) Standard.

>Support Ethernet service layer two switching and line speed forwarding of upstream and downstream services.

>Support frame filtering and suppression, support standard 802.1q Vlan function, support Vlan conversion.

>Support 4094 vlans (802.1q), support dynamic bandwidth allocation function (DBA).

>Support remote reset and restart functions

>Support restore factory parameters function, support data encryption

>Support GPON, EPON access

>Support WDM single fiber bidirectional (single fiber three way) transmission

> Rate: 2.5 Gbps / 1.25 Gbps

Certification: in accordance with CE, FCC, ROHS and other standards

EMC / EMI :Comply with VCCI Class B, FCC Part 15b standard

security:Comply with UL 60950 safety specification

Lightning protection against surge voltage protection:Itu-t k. 21 standard

Shenzhen GL-COM Technology CO.,LTD. , https://www.szglcom.com