Recently, with Intel, TSMC, and Samsung’s three giants each announced their participation in ASML, a semiconductor equipment manufacturer, they opened the curtain to a new generation of 450-mm (18-inch), ultra-ultraviolet lithography IC technology node. The four strong teams have jointly developed a new generation of IC technology to speed up the practicalization of equipment for the ultra-violet lithography machine. This is a model that has created a new model of global semiconductor cooperation. However, due to the timing, this cooperation may make it impossible. 18 inch IC line or eventually become tasteless. The risk may not come from the cooperation model itself, but more likely from the price cuts in semiconductor materials, the maturity of 3D IC technology, and other challenges.

The investment recovery period will be greater than 14 years. The total investment of the 18-inch technology node is expected to reach about 15 billion US dollars, and its investment recovery time will be longer than 14 years.

According to Chipworks' investment analysis, in the 12-inch wafer technology node stage, the total investment from R&D to mass production is US$12 billion, and the investment recovery period takes 14 years; and the total investment amount from the R&D to mass production of the 18-inch technology node is expected to be It will reach about 15 billion U.S. dollars and its investment recovery time will be longer.

According to reports, ASML has developed a detailed roadmap for the development of a new generation of ultra-violet lithography equipment and a 450mm wafer process. According to the ASML's technology roadmap, production time for 18-inch, ultra-violet photolithographic IC technology will be In 2018. Due to huge R&D expenses, ASML plans to sell 25% of its shares and in July this year sent an invitation to Intel, TSMC, and Samsung semiconductor manufacturers to invite the three giants to jointly develop new technology nodes.

At present, Intel has decided to invest USD 3.1 billion to acquire a 15% stake in ASML. TSMC has invested 838 million euros to obtain a 5% stake in ASML. Samsung has invested 503 million euros to buy a 3% stake in ASML. The three companies also invested 1 billion yuan at the same time. The US dollar, 276 million euros, and 276 million euros support the development of a new generation of lithography machines for ASML. According to reports, the current investment by the three giants is not enough for ASML. ASML needs to find other investors to send invitations to other semiconductor companies and sell the remaining 2% of shares.

Decrease in price of silicon material or influence of wafer size When high-purity silicon material no longer becomes the most important cost component, the trend of IC production lines to larger sizes may be affected.

Why IC wafers will grow bigger and bigger, from the initial 3 inches, 4 inches to 6 inches, 8 inches, 12 inches, and now they continue to advance to 18 inches non-stop? The main reason is due to the fact that the price of silicon material in the market is very expensive, usually up to hundreds of dollars per kilogram. Since the number of transistors included in a single IC chip is increasing, the area of ​​the IC chip is larger and larger, and the use of larger wafers is effective for wafers with larger area sizes such as CPUs and memories. The use of more area will effectively increase the utilization of silicon materials and significantly reduce the cost of silicon materials.

However, this basic premise may now be no longer valid. As more and more manufacturers have begun to master the production and purification of high-purity silicon materials, the price reduction trend of silicon materials has become inevitable. At present, the price of 11-12 "9" grade silicon materials used in the production of semiconductor devices has dropped from 600 US dollars to 800 US dollars / kg several years ago to about 80 US dollars / kg currently.

Historically, there have been phenomena that aluminum vessels are more expensive than gold vessels. Will this happen again between silicon materials and copper, iron and other materials? Although this situation is still unpredictable, we can infer that there are more silicon resources on the planet than iron resources and copper resources. With the future more manufacturers have mastered the purification and production technologies of silicon materials, as well as more advanced With the maturity of the new silicon refining technology, the significant price reduction of silicon materials has become a high probability event.

According to the ASML roadmap, the production time for 18-inch IC production lines is expected to be 2018. This period will continue for several years. The price of high-purity silicon materials will continue to decline as the popularity of advanced technologies continues to decline. After the most important cost components in production, the preconditions for IC manufacturers to invest heavily in the development and purchase of larger-scale IC production equipment will no longer be established, and IC manufacturing lines will eventually end up with larger-size development trends.

However, the silicon wafer size growth will not stop the trend of IC manufacturing technology continuing to develop to smaller line widths. The number of transistors included in a single IC chip will continue to grow according to Moore’s Law, ie, the number of transistors will increase every 18 months. Doubled, this trend will not change.

3D stacked IC manufacturing is another way to use 3D stacking and through-silicon via processes and packaging methods, which are more suitable for future SoC technology trends.

The new packaging technology of 3D stacked ICs has made great progress in recent years and will become another reason for the increase in the final wafer size. According to reports, the real mass production of 3D ICs will begin in 2013, and this will be a true revolution in IC manufacturing.

In the past, the heat dissipation of materials used in 3D IC stack packages was not enough. After using the 3D IC package, the operating temperature of the IC was too high, which resulted in the IC's performance stability being compromised. Now these problems have been basically overcome, and many companies have already launched IC products using 3D stacking technology. For example, IBM, Grooved, Micron, Intel, Samsung, and TSMC have all started to develop 3D IC stacking manufacturing technologies for mass production in a comprehensive and systematic way. Large-scale 3D stacking IC products are expected to start in 2013. Listed one after another.

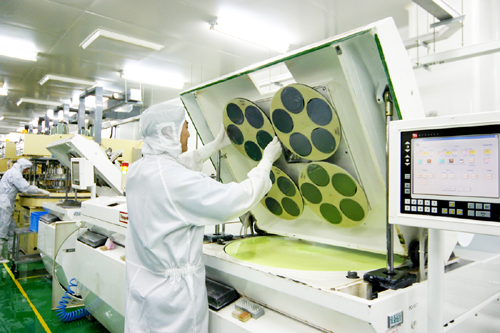

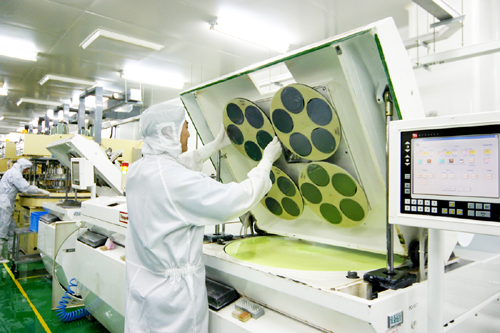

IC equipment manufacturers have also introduced a variety of 3D IC manufacturing equipment and packaging equipment for 8-inch wafers.

The world's major semiconductor organizations are all pushing forward with various standards for 3D ICs. The International Semiconductor Equipment Materials Industry Association has established four working groups dedicated to the development of 3D IC standards. Its 3DS-IC standards committee includes SEMI members such as Grooved, HP, IBM, Intel, and Samsung. The Semiconductor Manufacturing Alliance has established a 3D chip design center that includes Altera, ADI, LSI, ON Semiconductor, and Qualcomm. The Sematech Alliance also established a 300 mm 3D IC pilot line.

According to analysis, when the planar area of ​​a single IC is larger than two square centimeters, the average length of the connection between each functional area and the transistor is at least 10 times longer than the length of the connection using 3D multilayer wiring, and the delay time of information transmission is longer. Naturally, it will be much longer, which will greatly reduce the overall IC's speed and performance. Using the 3D layout and routing method, the individual chips are divided into small areas and taped, and then “assembled†using the 3D stacking and through-silicon via processes and packaging methods, which can reduce the average connection length and signal The delay time improves the performance of the IC and is more suitable for the future development trend of SoC technology.

However, ICs manufactured using these processes and packaging methods using 3D stacking and through-silicon vias may only be a transitional method. The 3D printing manufacturing technology that has already begun to emerge and is becoming increasingly practical is the ultimate 3D IC manufacturing method in the future. However, these methods can fundamentally increase the number of transistors in a unit volume without further development along the increasing direction of wafers.

The investment recovery period will be greater than 14 years. The total investment of the 18-inch technology node is expected to reach about 15 billion US dollars, and its investment recovery time will be longer than 14 years.

According to Chipworks' investment analysis, in the 12-inch wafer technology node stage, the total investment from R&D to mass production is US$12 billion, and the investment recovery period takes 14 years; and the total investment amount from the R&D to mass production of the 18-inch technology node is expected to be It will reach about 15 billion U.S. dollars and its investment recovery time will be longer.

According to reports, ASML has developed a detailed roadmap for the development of a new generation of ultra-violet lithography equipment and a 450mm wafer process. According to the ASML's technology roadmap, production time for 18-inch, ultra-violet photolithographic IC technology will be In 2018. Due to huge R&D expenses, ASML plans to sell 25% of its shares and in July this year sent an invitation to Intel, TSMC, and Samsung semiconductor manufacturers to invite the three giants to jointly develop new technology nodes.

At present, Intel has decided to invest USD 3.1 billion to acquire a 15% stake in ASML. TSMC has invested 838 million euros to obtain a 5% stake in ASML. Samsung has invested 503 million euros to buy a 3% stake in ASML. The three companies also invested 1 billion yuan at the same time. The US dollar, 276 million euros, and 276 million euros support the development of a new generation of lithography machines for ASML. According to reports, the current investment by the three giants is not enough for ASML. ASML needs to find other investors to send invitations to other semiconductor companies and sell the remaining 2% of shares.

Decrease in price of silicon material or influence of wafer size When high-purity silicon material no longer becomes the most important cost component, the trend of IC production lines to larger sizes may be affected.

Why IC wafers will grow bigger and bigger, from the initial 3 inches, 4 inches to 6 inches, 8 inches, 12 inches, and now they continue to advance to 18 inches non-stop? The main reason is due to the fact that the price of silicon material in the market is very expensive, usually up to hundreds of dollars per kilogram. Since the number of transistors included in a single IC chip is increasing, the area of ​​the IC chip is larger and larger, and the use of larger wafers is effective for wafers with larger area sizes such as CPUs and memories. The use of more area will effectively increase the utilization of silicon materials and significantly reduce the cost of silicon materials.

However, this basic premise may now be no longer valid. As more and more manufacturers have begun to master the production and purification of high-purity silicon materials, the price reduction trend of silicon materials has become inevitable. At present, the price of 11-12 "9" grade silicon materials used in the production of semiconductor devices has dropped from 600 US dollars to 800 US dollars / kg several years ago to about 80 US dollars / kg currently.

Historically, there have been phenomena that aluminum vessels are more expensive than gold vessels. Will this happen again between silicon materials and copper, iron and other materials? Although this situation is still unpredictable, we can infer that there are more silicon resources on the planet than iron resources and copper resources. With the future more manufacturers have mastered the purification and production technologies of silicon materials, as well as more advanced With the maturity of the new silicon refining technology, the significant price reduction of silicon materials has become a high probability event.

According to the ASML roadmap, the production time for 18-inch IC production lines is expected to be 2018. This period will continue for several years. The price of high-purity silicon materials will continue to decline as the popularity of advanced technologies continues to decline. After the most important cost components in production, the preconditions for IC manufacturers to invest heavily in the development and purchase of larger-scale IC production equipment will no longer be established, and IC manufacturing lines will eventually end up with larger-size development trends.

However, the silicon wafer size growth will not stop the trend of IC manufacturing technology continuing to develop to smaller line widths. The number of transistors included in a single IC chip will continue to grow according to Moore’s Law, ie, the number of transistors will increase every 18 months. Doubled, this trend will not change.

3D stacked IC manufacturing is another way to use 3D stacking and through-silicon via processes and packaging methods, which are more suitable for future SoC technology trends.

The new packaging technology of 3D stacked ICs has made great progress in recent years and will become another reason for the increase in the final wafer size. According to reports, the real mass production of 3D ICs will begin in 2013, and this will be a true revolution in IC manufacturing.

In the past, the heat dissipation of materials used in 3D IC stack packages was not enough. After using the 3D IC package, the operating temperature of the IC was too high, which resulted in the IC's performance stability being compromised. Now these problems have been basically overcome, and many companies have already launched IC products using 3D stacking technology. For example, IBM, Grooved, Micron, Intel, Samsung, and TSMC have all started to develop 3D IC stacking manufacturing technologies for mass production in a comprehensive and systematic way. Large-scale 3D stacking IC products are expected to start in 2013. Listed one after another.

IC equipment manufacturers have also introduced a variety of 3D IC manufacturing equipment and packaging equipment for 8-inch wafers.

The world's major semiconductor organizations are all pushing forward with various standards for 3D ICs. The International Semiconductor Equipment Materials Industry Association has established four working groups dedicated to the development of 3D IC standards. Its 3DS-IC standards committee includes SEMI members such as Grooved, HP, IBM, Intel, and Samsung. The Semiconductor Manufacturing Alliance has established a 3D chip design center that includes Altera, ADI, LSI, ON Semiconductor, and Qualcomm. The Sematech Alliance also established a 300 mm 3D IC pilot line.

According to analysis, when the planar area of ​​a single IC is larger than two square centimeters, the average length of the connection between each functional area and the transistor is at least 10 times longer than the length of the connection using 3D multilayer wiring, and the delay time of information transmission is longer. Naturally, it will be much longer, which will greatly reduce the overall IC's speed and performance. Using the 3D layout and routing method, the individual chips are divided into small areas and taped, and then “assembled†using the 3D stacking and through-silicon via processes and packaging methods, which can reduce the average connection length and signal The delay time improves the performance of the IC and is more suitable for the future development trend of SoC technology.

However, ICs manufactured using these processes and packaging methods using 3D stacking and through-silicon vias may only be a transitional method. The 3D printing manufacturing technology that has already begun to emerge and is becoming increasingly practical is the ultimate 3D IC manufacturing method in the future. However, these methods can fundamentally increase the number of transistors in a unit volume without further development along the increasing direction of wafers.

Cixi Xinke Electronic Technology Co., Ltd. , https://www.cxxinke.com